Released today, Synopsys built its solutions on the AMD Versal Premium VP1902 SoC to push the state of hardware-assisted verification (HAV).

Today, Synopsys announced a significant expansion of its hardware-assisted verification (HAV) portfolio to include new solutions based on the AMD Versal Premium VP1902 SoC. As AI, networking, and high-performance computing architectures scale beyond tens of billions of gates, HAV platforms are becoming more relevant than ever. Synopsys built its new solutions to make a dent in this marketplace.

The Synposys HAV portfolio

ZeBu-200: HAV Platform for Emulations Loads

The Synopsys ZeBu-200 is an HAV platform designed to accelerate emulation workloads with a performance increase of up to 2x compared to the previous ZeBu EP1 and EP2 systems. The solution provides a maximum scalable capacity of 15.4 billion gates, which is a 6x increase in capacity over prior generations.

Synopsys claims that a switch to the latest AMD Adaptive SoC technology is a major change for the ZeBu-200 compared to previous platforms.

“The difference in this particular announcement is that older versions were still based on the same AMD solutions,” De Schutter said. “It was more of a continuation of our lineup, where this release is really introducing new products based on a new part from AMD. The delta is much bigger than in the previous announcements.”

The ZeBu-200.

Along with a newly introduced ModelerHAV methodology, the ZeBu architecture increases scalability and support for larger design capacities than previous generations—up to 15.4 BG. By leveraging Synopsys' interface IP expertise, ZeBu-200 allows designers to partition multi-die or large AI workloads efficiently to simulate tens of billions of gates.

Synopsys says the ZeBu-200 improves debugging efficiency and reduces turnaround time for verification cycles with its unlimited waveform capture capabilities and interactive waveform reconstruction through the Synopsys Verdi debug environment. The system uses integrated multi-threaded simulation with virtualization to significantly accelerate software bring-up. It also accesses a broad ecosystem of transactor models, memory models, virtual system adaptors, and speed adaptors, facilitating flexible emulation across diverse applications.

HAPS-200: A Pre-Silicon Prototyping System

Synopsys has also released the HAPS-200 , a pre-silicon prototyping system that delivers high performance and scalability for complex hardware and software validation.

The HAPS-200 employs six AMD Versal Premium VP1902 SoCs fabricated on TSMC’s 7-nm process to support up to 32 interconnected systems. A heterogeneous platform, the system supports asynchronous clocking of different domains, where independent CPU, GPU, and interface operations can each operate at their respective maximum frequencies.

“For prototyping, performance is by far the most important capability,” De Schutter explained. “One of the key capabilities here is that we enable asynchronous clocking of different domains so your CPU or GPU can run independently from each other at the maximum clock frequency supported when mapping those designs onto the FPGAs.”

The architecture also leverages a direct-connect topology that optimizes interconnect latency and signal integrity for rapid prototyping. Because of this architecture, the system is said to offer 2x the performance, 3x the capacity, and 4x the debug bandwidth compared to previous-generation solutions.

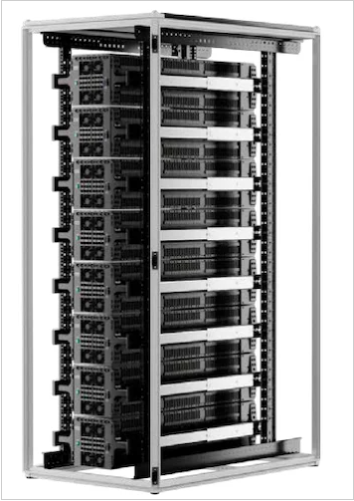

The HAPS-200 solution.

The HAPS-200 supports high-speed connectivity options, including QSFP, LVDS, MGB, USB3, and HT3 for integration with a variety of verification environments, and its rack-mountable design maximizes space efficiency through a vertical PCB placement with side-mounted connectors. The system consumes up to 2 kW of power and requires a 220-V supply.

For the workflow, the HAPS-200 supports the HAPS ProtoCompiler software, which integrates directly with the Verdi debug environment and uses a timing-driven synthesis engine to optimize FPGA partitioning and connectivity through the HapsTrak3 cabling system. The system supports multi-user and multi-design parallelization so teams can validate different design iterations simultaneously. When integrated with the ZeBu-200 synchronous clocking system, HAPS-200 offers emulation solutions for software bring-up, RTL regression, and power-performance analysis.

HAV and the Future of Semiconductor Design

Synopsys is bullish on HAPS and ZeBu because it believes that HAV systems will become necessary in semiconductor design.

“The industry as a whole has basically accepted that you need to do more on these hardware platforms to really get your verification done,” De Schutter said. “It's really the combination of all four of these factors—design size, software workload, verification scope, and system-level validation—that makes it a must to do that early in the design cycle.”